# IOWA STATE UNIVERSITY Digital Repository

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2013

# Automatic Energy Saving Schemes for Parallel Applications

Vaibhav Sundriyal Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd Part of the <u>Computer Engineering Commons</u>

### **Recommended** Citation

Sundriyal, Vaibhav, "Automatic Energy Saving Schemes for Parallel Applications" (2013). *Graduate Theses and Dissertations*. 13481. https://lib.dr.iastate.edu/etd/13481

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

### Automatic energy saving schemes for parallel applications

by

Vaibhav Sundriyal

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

Major: Computer Engineering

Program of Study Committee: Masha Sosonkina, Co-major Professor Zhao Zhang, Co-major Professor Philip Jones Ahmed Kamal

Mark Gordon

Iowa State University

Ames, Iowa

2013

Copyright © Vaibhav Sundriyal, 2013. All rights reserved.

### TABLE OF CONTENTS

| LIST OF TABLES      |                                                                             |     |  |  |

|---------------------|-----------------------------------------------------------------------------|-----|--|--|

| LIST OF FIGURES vii |                                                                             |     |  |  |

| ACKN                | OWLEDGEMENTS                                                                | xii |  |  |

| ABST                | RACT                                                                        | 1   |  |  |

| CHAP                | TER 1. INTRODUCTION                                                         | 2   |  |  |

| 1.1                 | Effects of Dynamic Voltage and Frequency Scaling and CPU Throttling on Com- |     |  |  |

|                     | munication                                                                  | 5   |  |  |

|                     | 1.1.1 Power Consumption Estimate for Multicore Nodes                        | 9   |  |  |

|                     | 1.1.2 Types of Distributed Communication Operations                         | 10  |  |  |

|                     | 1.1.3 Runtime System Encompassing Point-to-point and Collective Communi-    |     |  |  |

|                     | cations                                                                     | 11  |  |  |

| 1.2                 | Thesis Organization                                                         | 12  |  |  |

| CHAP                | TER 2. Energy-Aware Collective Communication Algorithms                     | 13  |  |  |

| 2.1                 | All-to-all                                                                  | 13  |  |  |

| 2.2                 | Allgather                                                                   | 16  |  |  |

| CHAP                | TER 3. Runtime Procedure                                                    | 19  |  |  |

| 3.1                 | Analysis                                                                    | 19  |  |  |

|                     | 3.1.1 Sequence                                                              | 20  |  |  |

|                     | 3.1.2 Watching                                                              | 22  |  |  |

|                     | 3.1.3 Recording                                                             | 22  |  |  |

|                     | 3.1.4 Scaling                                                               | 23  |  |  |

ii

| CHAP | TER 4  | 4. GAMESS                                         | 30 |

|------|--------|---------------------------------------------------|----|

| 4.1  | Overv  | iew of Quantum Chemistry Package GAMESS           | 30 |

| 4.2  | GAM    | ESS Energy Characteristics                        | 31 |

|      | 4.2.1  | The 4x4 Execution Configuration                   | 32 |

|      | 4.2.2  | The 4x1 Execution Configuration                   | 34 |

|      | 4.2.3  | Power profile of Self Consistent Field Phases     | 35 |

|      | 4.2.4  | Energy Consumption Model                          | 37 |

|      | 4.2.5  | Model Verification                                | 42 |

| 4.3  | Mapp   | ing                                               | 45 |

| CHAP | TER :  | 5. Modified Runtime System                        | 49 |

| 5.1  | Comm   | nunication Phase Detection                        | 49 |

| 5.2  | Syster | n Design                                          | 51 |

|      | 5.2.1  | Phase Detection                                   | 51 |

|      | 5.2.2  | Recording                                         | 53 |

|      | 5.2.3  | Frequency Scaling                                 | 53 |

| СНАР | TER (  | 6. Experimental Results                           | 61 |

| 6.1  | Energ  | y Aware Collective Communication Algorithms       | 63 |

| 6.2  | Runti  | me System                                         | 69 |

|      | 6.2.1  | Phase Characterization of the Applications Tested | 69 |

|      | 6.2.2  | NAS Benchmarks: Energy Savings with DVFS          | 70 |

|      | 6.2.3  | GAMESS: Energy Savings with DVFS                  | 72 |

|      | 6.2.4  | Throttling                                        | 76 |

| 6.3  | Modif  | ied Runtime System                                | 76 |

|      | 6.3.1  | Characterization of the Applications Tested       | 76 |

|      | 6.3.2  | CPU and Memory Power Consumption                  | 78 |

|      | 6.3.3  | Frequency Scaling with DVFS and Throttling        | 79 |

| CHAP | TER '  | 7. Related Work                                   | 84 |

| CHAPTER 8. Conclusions and Future Work | 88 |

|----------------------------------------|----|

| 8.1 Power Consumption Aware Techniques | 90 |

| 8.2 Frequency Scaling in GPUs          | 91 |

### LIST OF TABLES

| 1.1 | Given performance loss tolerance $\delta=10\%$ , the selection (Case) of core         |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | throttling levels (Level) based on the communication type (Type) and                  |    |

|     | message size (Size $\mathcal{L}$ ) from 0 to the largest possible $\hat{\mathcal{L}}$ | 9  |

| 4.1 | Input set of molecules.                                                               | 32 |

| 4.2 | Regression coefficients for determining the average power consumption                 |    |

|     | at a given frequency.                                                                 | 39 |

| 4.3 | CN and PE power for Saxitoxin direct mode.                                            | 43 |

| 4.4 | On-chip and off-chip times for input molecules in the FScal platform                  | 43 |

| 4.5 | CN energy consumption in the direct mode on three lower frequencies                   |    |

|     | for the input molecules in the FScal platform, normalized with respect                |    |

|     | to the highest frequency. Frequencies (in GHz) are $f_1 = 3.0, f_2 = 2.67$ ,          |    |

|     | $f_3 = 2.33$ , and $f_4 = 2.0$ .                                                      | 44 |

| 4.6 | Data substituted into the theoretical model to determine the feasibility              |    |

|     | of the CN energy consumption for different frequencies                                | 44 |

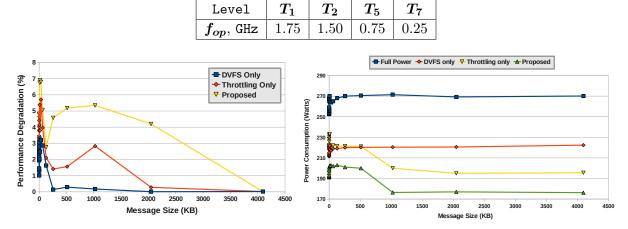

| 6.1 | Effective operational frequency $(f_{op})$ at a combination of the 2 GHz              |    |

|     | P-state and one of the T-states (Level) used.                                         | 64 |

| 6.2 | Average percentage of the EDP reductions in all the experiments for                   |    |

|     | the three energy saving strategies                                                    | 68 |

| 6.3 | Application characterizations by the runtime procedure. (The average                  |    |

|     | call and phase lengths, CallLen and PhaseLen, are given in microseconds.)             | 69 |

| 6.4 | Energy-delay product (EDP) values for the three proposed binding                         |    |  |

|-----|------------------------------------------------------------------------------------------|----|--|

|     | under the aggressive frequency scaling strategy normalized to the EDP                    |    |  |

|     | of the Disjoint-I binding operated at the highest frequency                              | 75 |  |

| 6.5 | Characterization of NAS, CPMD, and pARMS tests (column ${\bf TName})$                    |    |  |

|     | by the proposed runtime system. The number of phases detected is                         |    |  |

|     | shown in column $\mathbf{PhN}$ . The average call and phase lengths, $\mathbf{CLen}$ and |    |  |

|     | $\mathbf{PhLen},$ are in microseconds, respectively. The column $\mathbf{CTypes}$ gives  |    |  |

|     | the MPI call types as observed in the phases                                             | 78 |  |

www.manaraa.com

### LIST OF FIGURES

| 1.1 | DVFS (2 GHz) with different throttling states affecting idle power con-         |    |

|-----|---------------------------------------------------------------------------------|----|

|     | sumption of a node                                                              | 3  |

| 1.2 | MPI ping-pong test to determine the effect of the lowest DVFS (2 GHz) $$        |    |

|     | on the internode communication (left) and intranode communication               |    |

|     | (right). The performance loss percentage of the highest DVFS frequency          |    |

|     | is shown in the $y$ -axis                                                       | 6  |

| 1.3 | MPI ping-pong test to determine the effect of the lowest DVFS (2 GHz) $$        |    |

|     | and CPU throttling on intranode communication. Vertical lines indicate          |    |

|     | the message sizes at which the performance loss of $10\%$ is reached. $\ .$ .   | 7  |

| 1.4 | CPU throttling with DVFS at 2 GHz in internode communications for               |    |

|     | messages (left) smaller and (right) larger than 8 KB. Vertical line indi-       |    |

|     | cates the message size at which the performance loss of $10\%$ is reached.      | 8  |

| 2.1 | The first four communication steps of the Bruck Index all-to-all algo-          |    |

|     | rithm on three nodes with two sockets (shown as rectangles) and eight           |    |

|     | cores (ovals) each. Internode communications are shown as straight              |    |

|     | arrows across the node boundaries                                               | 14 |

| 2.2 | Energy saving strategy for the <i>all-to-all</i> operations with the throttling |    |

|     | level selection based on the message size (per Table 1.1)                       | 15 |

| 2.3 | Energy saving strategy for the <i>allgather</i> operations with the throttling  |    |

|     | level selection based on the message size (per Table 1.1)                       | 17 |

| 2.4 | The RA communication pattern for the block (left) and cyclic (right)            |    |

|     | rank placements. Arrows indicate the communication direction                    | 18 |

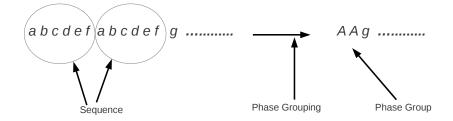

| 3.1 | Sequence recognition and phase grouping                                          | 20 |

|-----|----------------------------------------------------------------------------------|----|

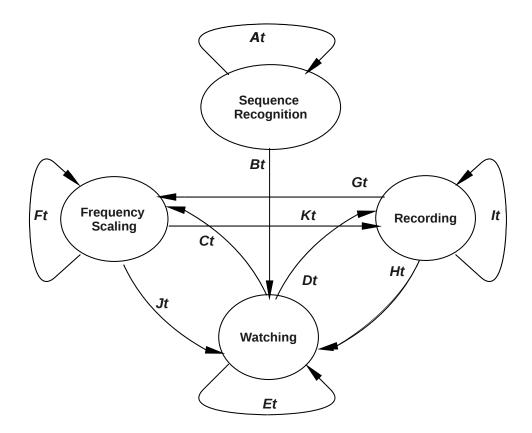

| 3.2 | State diagram for runtime procedure to apply energy savings efficiently.         |    |

|     | The transitions are labeled with $Lt$ , where $L$ takes a value of the first     |    |

|     | 11 letters of the alphabet The transition of a state into itself ( $At$ , $Et$ , |    |

|     | Ft, It) indicate ongoing state action                                            | 21 |

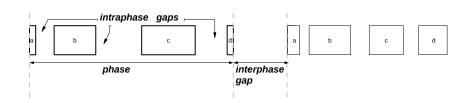

| 3.3 | Trace of an MPI application invoking eight MPI_Send and MPI_Recv                 |    |

|     | calls with a phase length of four. (The calls within a phase are ordered         |    |

|     | lexicographically from $a$ to $d$ .)                                             | 23 |

| 3.4 | An Intel Xeon E5450 processor within one socket, having four physical            |    |

|     | cores. A physical core has an L1 cache and a shared L2 cache, such that          |    |

|     | pairs of core processing units (PUs)—(P#0, P#4), (P#2, P#6)—each                 |    |

|     | share an L2 cache.                                                               | 26 |

| 3.5 | Overlapping of communication phases in a pair twin-cores that share              |    |

|     | the L2 cache. The phase boundaries are marked as vertical dashed and             |    |

|     | dash-dotted for core 0 and core 4, respectively                                  | 27 |

| 3.6 | Grouping of the communication phases detected for rank 0 of the MG               |    |

|     | NAS benchmark. The capital letters followed by the double dots rep-              |    |

|     | resent communication phases followed by interphase gaps, respectively.           |    |

|     | A single group (shown as solid oval) has been found and the two corre-           |    |

|     | sponding subsequences are enclosed into the ovals denoting this group.           | 28 |

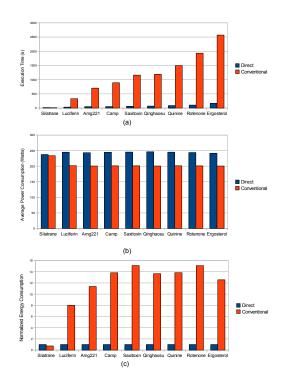

| 4.1 | 4x4 configuration: (a) Execution time, (b) Average power consumption,            |    |

|     | and (c) Energy consumption normalized with respect to the direct mode            |    |

|     | for the input molecules shown on the $x$ axes in the ascending order of          |    |

|     | their I/O requirements                                                           | 33 |

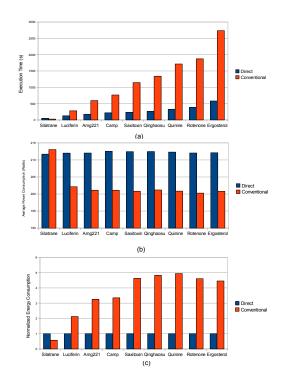

| 4.2 | 4x1 configuration: (a) Execution time, (b) Average power consumption,            |    |

|     | and (c) Energy consumption normalized with respect to the direct mode            |    |

|     | for the input molecules shown on the $x$ axes in the ascending order of          |    |

|     | their I/O requirements                                                           | 35 |

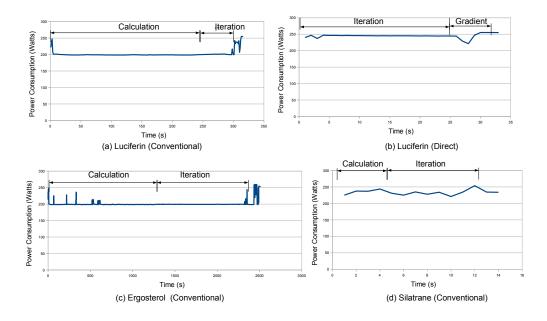

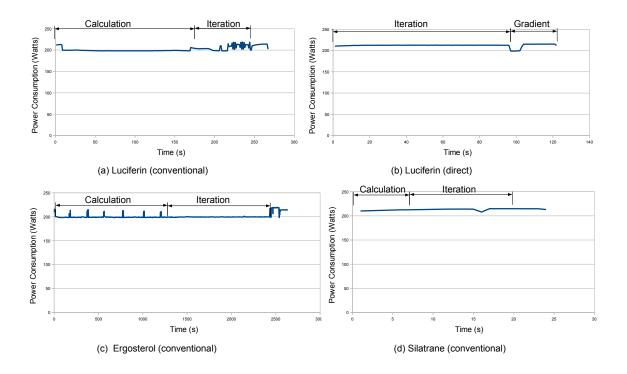

| 4.3 | Power profiles for some molecules in the 4x4 configuration. $\ldots \ldots 36$     |

|-----|------------------------------------------------------------------------------------|

| 4.4 | Power profiles for some molecules in the 4x1 configuration. $\dots \dots 37$       |

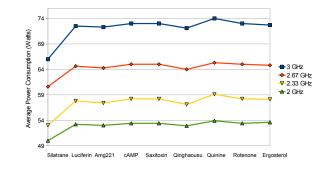

| 4.5 | Average power consumption of input molecules for direct mode on the                |

|     | four frequencies of FScal platform                                                 |

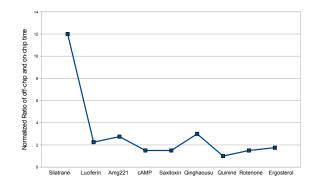

| 4.6 | Computation times ratio $\tau$ for input molecules normalized with $\tau$ for      |

|     | Quinine (FScal platform)                                                           |

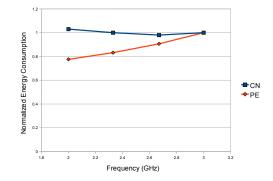

| 4.7 | Normalized energy consumption of PE and CN for Saxitoxin in direct                 |

|     | mode                                                                               |

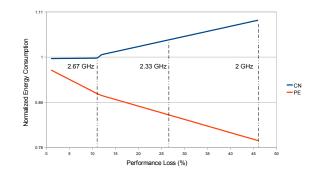

| 4.8 | Variation of energy consumption with performance loss for Saxitoxin in             |

|     | direct mode                                                                        |

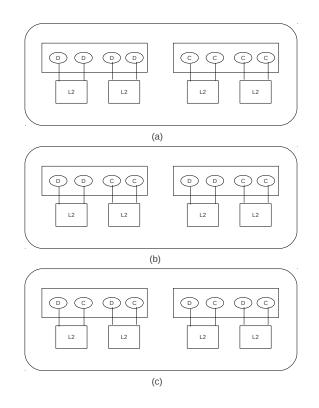

| 4.9 | Three bindings of GAMESS data server (D) and compute (C) processes:                |

|     | (a) Disjoint-I, (b) Disjoint-II, and (c) Slave, for Each compute node has          |

|     | two quad-core processors arranged as two sockets. Twin cores share the             |

|     | L2 cache                                                                           |

| 5.1 | Phase detection and string manipulation for master string with (a) con-            |

|     | secutive and (b) nonconsecutive communication phases 50 $$                         |

| 5.2 | State diagram for runtime system to apply frequency scaling efficiently.           |

|     | The transitions are labeled with $Lt$ , where $L$ takes a value $A–G$ . The        |

|     | transition of a state into itself $(At, Bt, Ct)$ indicate ongoing state action. 51 |

| 5.3 | Trace of an MPI application invoking eight MPI calls with a phase length           |

|     | of four. (The calls within a phase are ordered lexicographically from $a$          |

|     | to $d$ .)                                                                          |

| 5.4 | Grouping of the communication phases detected for rank 0 of the MG $$              |

|     | NAS benchmark. The capital letters followed by the double dots rep-                |

|     | resent communication phases followed by interphase gaps, respectively.             |

|     | A single group (shown as solid oval) has been found and the two corre-             |

|     | sponding subsequences are enclosed into the ovals denoting this group. 57          |

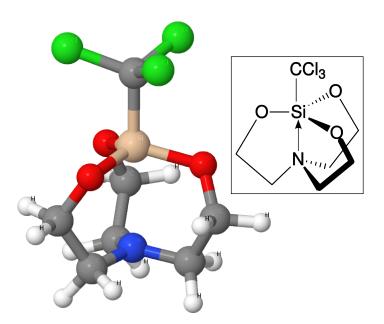

| 6.1 | 3D geometrical structure of the TCMS molecule (silicon, carbon, oxy-                                                               |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

|     | gen, nitrogen, chlorine and hydrogen atoms are shown as pink, gray,                                                                |    |

|     | red, blue, green, and white balls, respectively). The molecular skeletal                                                           |    |

|     | formula is inserted on the right                                                                                                   | 63 |

| 6.2 | The all-to-all performance degradation on $80$ cores (left) for three cases                                                        |    |

|     | and the power consumption across a compute node (right) for the four                                                               |    |

|     | cases: Executing at the highest frequency and no throttling (Full power);                                                          |    |

|     | only frequency scaling without throttling (DVFS $only$ ); only CPU throt-                                                          |    |

|     | tling without frequency scaling ${\tt Throttling\ only};$ and using the energy                                                     |    |

|     | saving strategies proposed for all-to-all (Proposed)                                                                               | 64 |

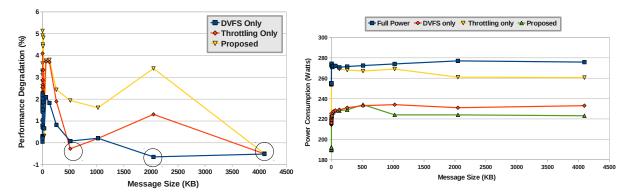

| 6.3 | The allgather performance degradation on 80 processes (left) for three                                                             |    |

|     | cases and the power consumption across a compute node (right) for the $% \mathcal{A}$                                              |    |

|     | four cases: Executing at the highest frequency and no throttling (Full $$                                                          |    |

|     | <pre>power); only frequency scaling without throttling (DVFS only); only</pre>                                                     |    |

|     | $\operatorname{CPU}$ throttling without frequency scaling ${\tt Throttling}$ only; and using                                       |    |

|     | the energy saving strategies proposed for all<br>gather ( ${\tt Proposed}).$                                                       | 66 |

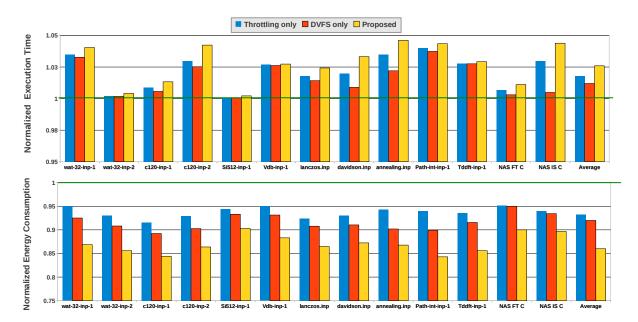

| 6.4 | Execution time (top) and energy consumption (bottom) of 11 CPMD $$                                                                 |    |

|     | inputs on 80 cores and of 2 NAS benchmarks on 64 processes for the                                                                 |    |

|     | DVFS only, Throttling only, and Proposed cases normalized to the                                                                   |    |

|     | Full power. The last set of bars (Average) represent the average of                                                                |    |

|     | the respective $y\text{-}\mathrm{axis}$ values across all the CPMD and NAS tests                                                   | 67 |

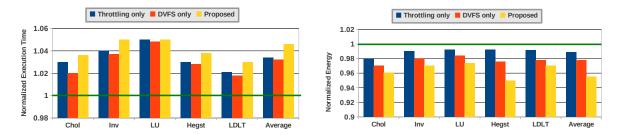

| 6.5 | Execution time (left) and energy consumption (right) of five Elemen-                                                               |    |

|     | tal algorithms—Cholesky (Chol), Triangular inverse (Inv), LU decom-                                                                |    |

|     | position (LU), Hermitian eigensolver (Hegst), and $\text{LDL}^T$ factorization                                                     |    |

|     | (LDLT)—on $80\ {\rm cores}\ {\rm for}\ {\rm the}\ {\tt DVFS}\ {\tt only}, {\tt Throttling}\ {\tt only}, {\rm and}\ {\tt Proposed}$ |    |

|     | cases normalized to the Full power. The last set of bars $({\tt Average})$                                                         |    |

|     | represent the average of the respective $y$ -axis values across the five Ele-                                                      |    |

|     | mental algorithms.                                                                                                                 | 68 |

х

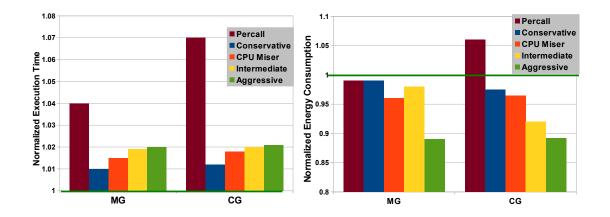

| 6.6  | Execution time and energy consumption of the NAS MG and CG bench-                           |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | marks for the different DVFS strategies normalized to the case when all                     |    |

|      | the processes operate at the highest frequency. (Results below 1 are                        |    |

|      | better.)                                                                                    | 71 |

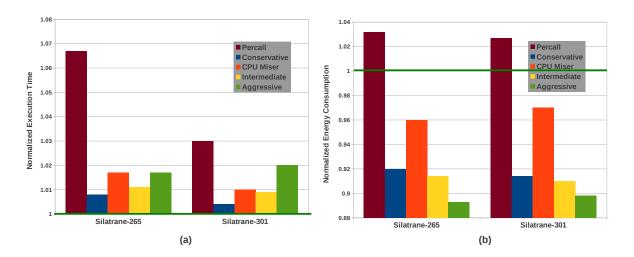

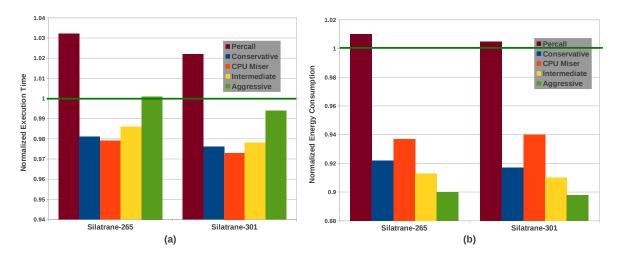

| 6.7  | (a) Execution time and (b) energy consumption of the two Silatrane                          |    |

|      | computations under ${\bf Disjoint-I}$ process mapping for the different DVFS                |    |

|      | strategies, normalized to the case when Disjoint-I binding is operated                      |    |

|      | at the highest frequency. (Results below 1 are better.) $\ldots \ldots \ldots$              | 73 |

| 6.8  | (a) Execution time and (b) energy consumption of the two Silatrane                          |    |

|      | computations under ${\bf Slave}$ process mapping for the different DVFS                     |    |

|      | strategies, normalized to the case when Disjoint-I binding is operated                      |    |

|      | at the highest frequency. (Results below 1 are better.) $\ldots$                            | 74 |

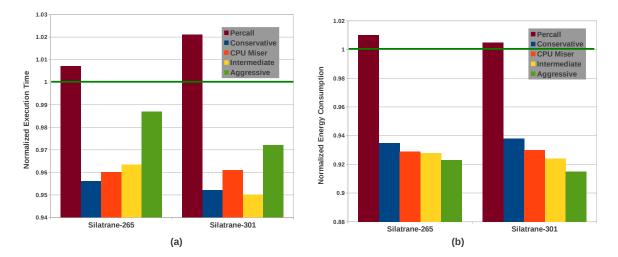

| 6.9  | (a) Execution time and (b) energy consumption of the two Silatrane                          |    |

|      | ${\rm computations\ under\ Disjoint-II}\ {\rm process\ mapping\ for\ the\ different\ DVFS}$ |    |

|      | strategies, normalized to the case when Disjoint-I binding is operated                      |    |

|      | at the highest frequency. (Results below 1 are better.) $\ldots$                            | 75 |

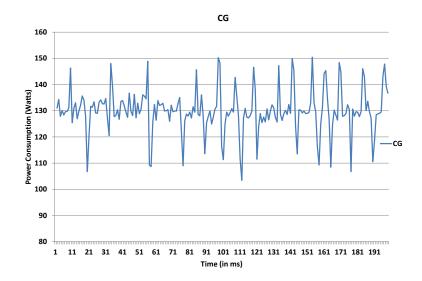

| 6.10 | CPU power consumption for CG benchmark.                                                     | 79 |

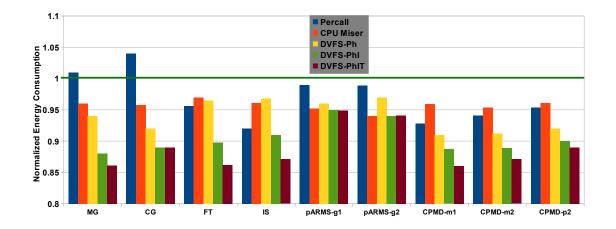

| 6.11 | Normalized execution time of the NAS, pARMS, and CPMD tests for                             |    |

|      | the different frequency scaling strategies. (Results below 1 are better.)                   | 81 |

| 6.12 | Normalized energy consumption of the NAS, pARMS, and CPMD tests                             |    |

|      | for the different frequency scaling strategies. (Results below 1 are better.)               | 82 |

| 8.1  | Frequency scaling range for the K20 Tesla GPU obtained through nvidia- $$                   |    |

|      | smi                                                                                         | 91 |

### ACKNOWLEDGEMENTS

I am very grateful to Dr. Masha Sosonkina for being an understanding guide who is always willing to hear the other person and, for supporting me through ups and downs of my research. I thank her for her numerous hours spent on revising the manuscripts to bring them to the highest standards — providing me an invaluable learning experience in the process. She has always managed to give me time for discussions in spite of her busy schedule, yet, our meetings have never been during the late hours or the weekends. This balanced approach towards work and personal life is one of the most admirable things about her. I am also grateful to Dr. Zhao Zhang for providing me useful inputs in my research through out my stint at Ames Laboratory. His lectures proved to be a major factor in choosing my area of research for this thesis.

I am very thankful to my other committee members Dr. Philip Jones, Dr. Ahmed Kamal and Dr. Mark Gordon for their valuable time and inputs on my research. I am very thankful to my lab members for providing me with a friendly environment and for their support in my research. I thank all the departmental staff for their timely help.

I gratefully acknowledge the support received from in part by Ames Laboratory and Iowa State University under the contract DE-AC02-07CH11358 with the U.S. Department of Energy, by the Air Force Office of Scientific Research under the AFOSR award FA9550-12-1-0476, and by the National Science Foundation grants NSF/OCI—0941434, 0904782, 1047772.

I am very grateful to my parents and family members for supporting me to come here for PhD and, for their love and care in my life.

I am very grateful to God for always arranging the best for me and for all the gifts in life. I am very grateful to my friends in Ames, whose unconditional support has helped me in countless ways in my PhD and in leading a wholesome life.

### ABSTRACT

Although high-performance computing traditionally focuses on the efficient execution of large-scale applications, both energy and power have become critical concerns when approaching exascale. Drastic increases in the power consumption of supercomputers affect significantly their operating costs and failure rates. In modern microprocessor architectures, equipped with dynamic voltage and frequency scaling (DVFS) and CPU clock modulation (throttling), the power consumption may be controlled in software. Additionally, network interconnect, such as Infiniband, may be exploited to maximize energy savings while the application performance loss and frequency switching overheads must be carefully balanced. This work first studies two important collective communication operations, all-to-all and allgather and proposes energy saving strategies on the per-call basis. Next, it targets point-to-point communications to group them into phases and apply frequency scaling to them to save energy by exploiting the architectural and communication stalls. Finally, it proposes an automatic runtime system which combines both collective and point-to-point communications into phases, and applies throttling to them apart from DVFS to maximize energy savings. The experimental results are presented for NAS parallel benchmark problems as well as for the realistic parallel electronic structure calculations performed by the widely used quantum chemistry package GAMESS. Close to the maximum energy savings were obtained with a substantially low performance loss on the given platform.

www.manaraa.com

### CHAPTER 1. INTRODUCTION

The last few decades have witnessed a tremendous rise in the design of scalable applications for various scientific domains. Their computational requirements force system engineers to develop ever more performance-efficient architectures. As a result, power consumption is rapidly becoming a critical design constraint in modern high-end computing systems. For example, according to an U.S. Department of Energy guidelines [48], to sustain an exaflops machine, its power consumption cannot go beyond ten-fold that of the current petaflops machines, meaning that for a 1000-fold increase in performance, the increase in power consumption may not accede ten-fold. Moreover, if the focus of the high-performance computing (HPC) community is only to maximize application performance, the computing system operating costs and failure rates can reach prohibitive levels.

A wide range of HPC applications rely on the communication libraries implementing the Message Passing Interface<sup>1</sup> (MPI), which has become a *de facto* standard for the design of parallel applications. It defines both point-to-point and collective communication primitives widely used in parallel applications. Researchers in the past have proposed energy-aware techniques in MPI [35, 17] by identifying communication phases in the execution of parallel application which are not compute intensive and then applying dynamic voltage and frequency scaling (DVFS) during those phases. However, most of these studies do not apply energy saving strategies *within* collective operations. For example, in [35], authors identify the communication phase as several MPI calls, all lasting long enough to apply DVFS without a significant overhead.

Conversely, collective operations are studied in this work on the *per-call* (fine-grain) basis as opposed to a "black-box" approach, which treats communication phase as indivisible operation contributing to the parallel overhead. The appeal of fine-grain *per-call* approach to energy

<sup>&</sup>lt;sup>1</sup>MPI Forum: http://www.mpi-forum.org

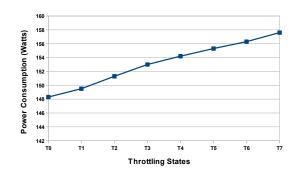

Figure 1.1 DVFS (2 GHz) with different throttling states affecting idle power consumption of a node.

saving grows with the advent of large-scale computing platforms in which the the number of communicating processes is increasing rapidly. In particular, for such platforms a collective operation would amount to a large multitude of point-to-point communications grouped together and essentially present a communication phase in itself. Furthermore, to retain algorithmic efficiency, energy saving strategies are being incorporated within the *existing* algorithms used for executing the collective operations. In this work, the initial steps of which were described in [53], both the type of a collective communication and the amount of data to be transferred are considered to obtain energy saving with the DVFS in conjunction with the CPU throttling. Being widespread in parallel applications, the all-to-all and allgather operations are addressed here. By definition, a collective operation requires the participation of all the processes in a given communicator. Hence, such operations incur a significant amount of the network phase during which there exist excellent opportunities for applying energy saving techniques, such as DVFS and CPU throttling.

**CPU Throttling and Idle Power Consumption.** It was noticed that idle power consumption of a node increases as a higher level of throttling is applied. In the idle state of the system a loop executes which consists of the HLT assembly language instruction to save power. For example, Fig. 1.1 shows the change in the idle power consumption of a node at 2 GHz with various T-states. Note that, although the idle power of a node refers to the power consumed when the processor is idle, an augmentation in the T-states increases this power. This increase may be attributed to the CPU throttling causing the CPU to reach a higher CPU power mode,

also called C-state<sup>2</sup>, less often and, thus, to draw more power. The operating system kernel installed on the node does not have a tickless scheduler and has frequency of 1000 Hz. Not having a tickless scheduler may also affect this power consumption as suggested in [49], for example. However, contrary to a popular view that throttling is useless for the processors equipped with DVFS and despite this negative effect, it is a viable option when used in conjunction with DVFS.

CPU Throttling and Dynamic Voltage and Frequency Scaling(DVFS) in Intel Architectures. The current generation of Intel processors provides various P-states for DVFS and T-states for throttling. In particular, the Intel "Core" microarchitecture, which provides four P-states and eight T-states from  $T_0$  to  $T_7$ , where state  $T_j$  refers to introducing j idle cycles per eight cycles in CPU execution. The delay of switching from one P-state to another can depend on the current and desired P-state and is discussed in [41]. The user may write a specific value to model-specific registers (MSRs) to change the P- and T-states of the system.

The CPU throttling can be viewed as equivalent to dynamic frequency scaling (DFS) [4] because, by inserting a given number of idle cycles in the CPU execution, a particular operating frequency is obtained without changing the operating voltage of the cores. Hence, DFS is less effective than DVFS in terms of power saving but, when used with conjunction with DVFS, it may result in significant reduction of power across a compute node.

Notes on Infiniband. The Infiniband interconnect has become one of most popular standards marking its presence in more that 43% of the systems in the TOP 500<sup>3</sup> list. Several network protocol layers are offloaded to the host channel adapters (HCA) in an Infiniband<sup>4</sup> network. Here, MVAPICH2<sup>5</sup> implementation of MPI, which is designed for Infiniband networks, is considered. Infiniband offers two modes of message progression: polling and blocking. Even though blocking mode consumes less power than polling, a lower communication overhead is

<sup>&</sup>lt;sup>5</sup>http://mvapich.cse.ohio-state.edu

<sup>&</sup>lt;sup>2</sup>Advanced Configuration and Power Interface: http://www.acpi.info

<sup>&</sup>lt;sup>3</sup>http://www.top500.org

<sup>&</sup>lt;sup>4</sup>http://www.infinibandta.org

incurred with the polling mode, in which an MPI process constantly samples for the arrival of a new message rather than the with blocking, which causes CPU to wait for an incoming message. Therefore, MVAPICH2 uses the polling communication mode by default. A detailed comparison of these two modes for the all-to-all operation is done in [27], where the high overhead introduced by blocking mode is demonstrated. Additionally, on the platform used in this work, the average performance loss observed was 19%–340% with power savings of 2%–34% for the blocking mode when compared to polling one.

# 1.1 Effects of Dynamic Voltage and Frequency Scaling and CPU Throttling on Communication

Since collective operations are developed on top of point-to-point communication operations, it is reasonable to analyze first the DVFS and CPU throttling effects on the latter operations. In particular, this section explores possibilities to apply these frequency scaling techniques with respect to two factors, message size and communication type (inter- or intranode), which are deemed to affect significantly the energy saving potential in any multicore computing environment. Although the investigation was performed with a certain Intel processor architecture using the Infiniband to connect the nodes, the obtained results lead nevertheless to general conclusions since there were no assumptions made on particular values or the number of the C-states (only their relative ordering was used).

According to the theoretical models [59] estimating the time spent in a collective operation, any increase in the point-to-point communication time should proportionally increase the time spent in the collective operation. Therefore, a user may judiciously choose a performance loss for the collectives by analyzing the behavior of point-to-point communications. Then appropriate DVFS and CPU throttling levels may be selected to minimize the energy consumption during a collective operation with the chosen performance loss. In this work, a performance loss threshold of  $\delta=10\%$  is considered and the collective communication algorithms are studied in detail to exploit opportunities for energy savings within them on a fine-grain level. Alternatively, one may consider the so-called energy-delay product (EDP) and its variants in order to

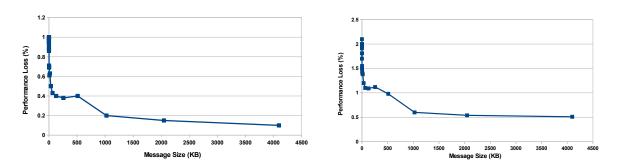

Figure 1.2 MPI ping-pong test to determine the effect of the lowest DVFS (2 GHz) on the internode communication (left) and intranode communication (right). The performance loss percentage of the highest DVFS frequency is shown in the *y*-axis.

measure the energy savings (see, e.g., [37]). EDP has a clear advantage over measuring "raw" power consumption since it accounts for the execution time as well. So, there is no temptation to run an application as slow as possible to gain in energy efficiency. Although EDP is a preferred general-use metric for high-performance applications, adhering to a performance loss tolerance set by a knowledgeable application user or keeping the performance loss as small as possible may work just as rigorously.

Fig. 1.2(left) and Fig. 1.2(right) depict the degradation in the point-to-point internode and intranode communication time, respectively, when two communicating processes are operated at the the lowest frequency as compared with the highest. A ping-pong communication test is chosen to evaluate the effect of frequency scaling because this is a typical way to use pointto-point communications in MPI. The plots in Fig. 1.2 show the average performance loss of about 1%; thus, the effect of the DVFS on both internode and intranode point-to-point communications is minimal. Therefore, they can safely be operated at the lowest frequency of the processor. It can be noted here that the DVFS and CPU throttling for evaluating point-to-point communications were applied only on the cores on which the processes were executing.

If a DVFS switch is applied for every single communication call, it may result in a significant performance loss because of the DVFS overhead which is present in the majority of the commodity processor types from Intel and AMD processor types. For this reason, the research in [35] focuses on developing a phase-detection framework that dynamically identifies the communications phases in an application and applies DVFS per phase rather than per

Figure 1.3 MPI ping-pong test to determine the effect of the lowest DVFS (2 GHz) and CPU throttling on intranode communication. Vertical lines indicate the message sizes at which the performance loss of 10% is reached.

communication call. For collective communications, however, the impact of DVFS overhead on overall performance decreases rapidly as the number of communicating cores increases because the collectives may be viewed as a bundle of several point-to-point communications from an algorithm implementation viewpoint.

Selecting Appropriate CPU Throttling Levels. Since DVFS reduces both frequency and voltage of the processor cores, it saves more power than CPU throttling, which reduces only the frequency, if both are used separately. Thus, DVFS should be always reduced first to its lowest value and only after that the throttling level should be increased.

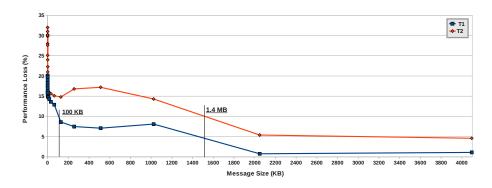

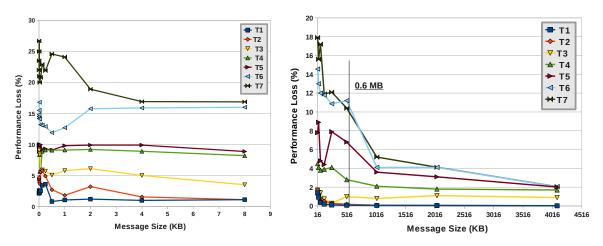

The drawback of the CPU throttling is that it may result in significant performance loss for the intranode communication. Fig. 1.3 depicts the performance degradation in intranode pointto-point communication from the case when the communicating cores operate at the highest frequency to the one at the lowest frequency, while in different T-states. The results are shown for the states  $T_1$  and  $T_2$  only because higher T-states produce a performance degradation greater than 10% for all the message sizes. By comparing Fig. 1.2(right) and Fig. 1.3, it is observed that, with just one idle CPU cycle, the average performance loss increases from 1.5% to 15%. Fortunately, as the message size grows, the performance loss decreases when CPU throttling is applied, which also has been noticed in [36].

Fig. 1.4 shows the performance degradation in the *internode* communication time with DVFS and various throttling states. This communication time is much less affected by the

Figure 1.4 CPU throttling with DVFS at 2 GHz in internode communications for messages (left) smaller and (right) larger than 8 KB. Vertical line indicates the message size at which the performance loss of 10% is reached.

CPU throttling as compared with the intranode communication because, for the internode message transfers, the remote dynamic-memory access (RDMA) offloads a large part of the communication processing to the network interface cards (NICs) (see [36]). Thus, the processor involvement in internode message transfers is minimal and higher throttling states may be used safely.

Fig. 1.3 indicates (see vertical lines) that the performance loss is no higher than 10% when the throttling state  $T_1$  is applied to the messages greater than 100 KB and, after the 1.4 MB, the state  $T_2$  may be used during the *intranode communication*. Similarly, from Fig. 1.4, it may be inferred that 0.6 MB is the message size corresponding to the throttling level switch (from  $T_5$ to  $T_7$ ) so the chosen performance loss is not exceeded for the *internode* communication. If a processing core is not involved in any communication during the collective operation, then it can be operated at the highest throttling level  $T_7$ . It can be noted that performance loss of 10% is the maximum performance loss that an application suffers from since the collective communication may form only a portion of the parallel execution of that application.

For the given computing environment and performance loss of 10%, Table 1.1 summarizes the appropriate CPU throttling levels depending on the type of communication and message size. In a different environment, the message size intervals and the throttling level numbers may differ. However, the deduced general principles of the DVFS and CPU throttling application

Table 1.1 Given performance loss tolerance  $\delta = 10\%$ , the selection (Case) of core throttling levels (Level) based on the communication type (Type) and message size (Size  $\mathcal{L}$ ) from 0 to the largest possible  $\hat{\mathcal{L}}$ .

| <br>$\sim$ |           |                                         |       |  |  |  |

|------------|-----------|-----------------------------------------|-------|--|--|--|

| Case       | Туре      | Size $\mathcal L$                       | Level |  |  |  |

| Ι          | Intranode | [100KB, 1.4MB]                          | $T_1$ |  |  |  |

| II         | Intranode | $[1.4\text{MB}, \hat{\mathcal{L}}]$     | $T_2$ |  |  |  |

| III        | Internode | [1B, 0.6MB[                             | $T_5$ |  |  |  |

| IV         | Internode | $[0.6 \mathrm{MB},  \hat{\mathcal{L}}]$ | $T_7$ |  |  |  |

| V          | None      | 0                                       | $T_7$ |  |  |  |

will hold. Specifically,

- DVFS may remain at the lowest state during the entire communication regardless of the message size.

- Intranode communications may suffer from high throttling levels. while the internode communications are not affected as much by throttling.

- For the intranode, choose the lowest T-state for small message sizes, while the next level up may be selected for bigger ones.

- For the internode, choose the highest T-state for large message sizes and decrease it for small messages.

- If a core is idle during the communication it may be operated at the highest T-state.

Finally, note that collective communications are blocking in nature and, therefore, reducing the processor frequency during their operation will not slow down the computational portion of an application.

#### 1.1.1 Power Consumption Estimate for Multicore Nodes.

Both DVFS and CPU throttling are employed in this work to obtain energy saving, so there is need to understand the relationship between these two techniques and their relative efficacy. In addition, it would be beneficial to predict how the proposed energy saving strategies work a platform with a large number of cores. Therefore, a theoretical power consumption estimate is presented and experimentally verified here for a multicore node.

Let a multicore compute node have frequencies  $f_i$ , (i = 1, ..., m), such that  $f_1 < ... < f_m$ , and throttling states  $T_j$ , (j = 0, 1, ..., n). When all the *c* cores of the node execute an application

at the frequency  $f_i$ , each core consumes the dynamic power  $p_i$  proportional to  $f_i^3$  as has been shown in [9]. Let  $P_{i,j}$  be the power consumed by the entire node at the frequency  $f_i$  and throttling state  $T_j$ ;  $\bar{P}_{i,j}$  be the total *idle* power consumption of a node at the frequency  $f_i$  and throttling level  $T_j$ , and  $P_d$  be the dynamic power consumption of the compute node components different from the processor (e.g., memory, disk, and NIC). Then, the power consumption of a node with no idle cycles, i.e., at  $T_0$ , may be defined as

$$P_{i,0} = c \times p_i + \bar{P}_{i,0} + P_d \tag{1.1}$$

to give an idea how the frequency scaling affects the power consumption. This expression may vary with the application characteristics since each application may have a different power consumption pattern depending of its utilization of the compute node components. When the nonzero level of throttling  $T_j$ ,  $(j \neq 0)$  is used, equation Equation (1.1) becomes

$$P_{i,j} = \frac{j \times (\bar{P}_{i,j} + P_d) + (n-j)P_{i,0}}{n} .$$

(1.2)

To determine the idle power consumption of a node  $P_{i,j}$ , Fig. 1.1 and equation Equation (1.2) may be used. For example, the node power consumptions at the lowest frequency  $f_1$  and no throttling,  $P_{1,0}$ , and with the  $T_7$  throttling level,  $P_{1,7}$ , are 148 and 158 watts, respectively, according to Fig. 1.1. Then, the idle power  $\bar{P}_{1,7}$  at  $f_1$  and  $T_7$  is found to be around 160 watts by substitution into equation Equation (1.2) and with assumptions of eight T-states and no dynamic power consumption. To predict the entire node power for the proposed energy saving strategies, the  $P_d$  of such components as memory and NICs has to be also considered. For the memory dynamic power consumption, an extrapolation method discussed in [15] has been used to obtain 10 watts consumed by memory in the all-to-all operation for 1 MB message size.

#### 1.1.2 Types of Distributed Communication Operations

A collective operation is considered as a multitude of point-to-point communications grouped together, essentially presenting a single communication stream. Since the rank<sup>6</sup> sequences of

<sup>&</sup>lt;sup>6</sup>For the sake of brevity throughout this work, the "rank" will denote either the destination or source neighbor rank depending on whether the sending or receiving operation is considered, respectively.

the point-to-point transfers within a collective communication are typically known during the collective algorithm execution, the places to apply DVFS and throttling may be determined in advance for a given message size. For example, an *a priori* algorithmic analysis of the MPI\_Alltoall algorithms reveals that, for a few initial iterations, every core undergoes intranode communications after which the communication becomes purely internode. Thus, different throttling states may be preselected while the DVFS is lowered to the maximum at the start of MPI\_Alltoall and raised back to the highest level in the end. A single point-to-point communication is, on the other hand, just one call per given processor rank. Therefore, its frequency scaling on the percall basis, as was done for collectives, may easily result in a significant parallel performance degradation due to the switching overhead. Nevertheless, it is desirable to decrease the energy consumption during the point-to-point communications, in addition to collectives, because they may constitute a significant portion of the execution (often more than 10%); and applications communicating heavily in the point-to-point fashion are abundant. Therefore, this work focuses on a class of point-to-point communications as provided by the MPI standard.

By considering test cases from the NAS benchmark suite [5], this work validates a proposed runtime procedure that groups several point-to-point communications, aiming to reduce the overhead from the DVFS and throttling. Next, it applies this procedure to realistic electronic structure calculations performed by the widely-used GAMESS quantum chemistry package [20, 47], which is capable of performing molecular structure and property calculations by a rich variety of *ab initio* methods. An estimated user base of 150,000 comes from more than 100 countries. The GAMESS communication library, which has been custom-built, is based on the partitioned global address space (PGAS) concepts.

# 1.1.3 Runtime System Encompassing Point-to-point and Collective Communications

The phase-detection mechanism proposed in [56] cannot be simply extended to encompass both point-to-point and collective communications and the proposed frequency scaling strategies did not combine DVFS and throttling. A modified runtime system is proposed here that detects communication phases in parallel applications transparently to the application code and com-

munication library and without any prior knowledge of the parallel application communication characteristics. Once the communication phases are detected, a particular frequency is chosen based on the proposed frequency scaling strategies and the library-specific implementations of communication calls. To illustrate the latter, a few examples from an MPI implementation of collective calls are provided. By considering test cases from the NAS benchmark suite [5], as well as real-world applications in molecular dynamics (CPMD<sup>7</sup>) and iterative parallel linear system solver (pARMS [34]), the proposed runtime system is validated.

### 1.2 Thesis Organization

This thesis is organized as follows: In Chapter 2, the design and implementation of energy aware collective communication algorithms is discussed.

In Chapter 3, the runtime procedure to obtain energy saving in point-to-point communications is proposed.

In chapter 4, the energy characteristics and the application of the runtime procedure to the quantum chemistry software GAMESS is discussed.

In Chapter 5, the modified design of the runtime procedure which applies frequency scaling to both point-to-point and collective communications is discussed.

In Chapter 6, the experimental results are presented.

In Chapter 7, existing related works are reviewed.

In Chapter 8, the conclusions and future work regarding obtaining energy saving in GPUs is discussed.

الم للاستشارات

### CHAPTER 2. Energy-Aware Collective Communication Algorithms

In this chapter, the algorithms for two collective operations, all-to-all and allgather as implemented in MVAPICH2, are studied and strategies are proposed to minimize the energy consumption during their algorithmic steps. For the findings from Section 1.1 to be employed here, the intra- and internode communication types need to be determined within the collective algorithms used as well as different message sizes considered in their implementations. Thus, the proposed strategies will contain stages in accordance with the communication types and each stage will have several cases based on possible message sizes.

Rank placement is directly related to the communication type. MVAPICH2 provides two formats of rank placements on multicores, namely *block* and *cyclic*. In the block strategy, ranks are placed such that any node j (j = 0, 1, ..., N - 1) having c cores contains ranks from  $c \times j$ to  $c \times (j + 1) - 1$ . In the cyclic strategy, all the ranks i belong to j if ( $i \mod N$ ) equals j. The block rank placement has been chosen for the rest of the work due to several considerations, outlined in the end of this section.

### 2.1 All-to-all

The MVAPICH2 implementations of all-to-all are based on three algorithms: 1) Bruck Index, used for small (less than or equal to 8KB) messages with at least eight participating processes; 2) Pairwise Exchange, used for large messages and when the number of processes is a power of two; 3) Send To rank i + k and Receive From rank i - k, used for all the other processor numbers and large messages. These algorithms are referred further in text as BIA, PEA, and STRF, respectively.

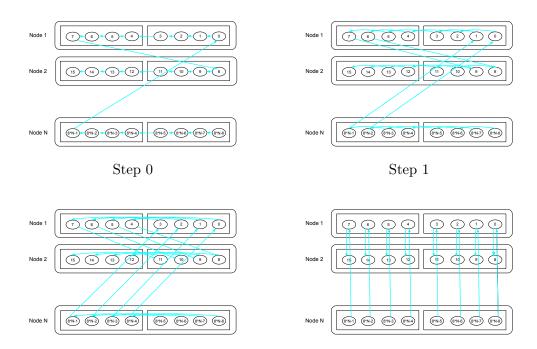

Figure 2.1 The first four communication steps of the Bruck Index all-to-all algorithm on three nodes with two sockets (shown as rectangles) and eight cores (ovals) each. Internode communications are shown as straight arrows across the node boundaries.

Step 3

Step 2

**Bruck Index Algorithm** first makes a local copy and then does an upward shift of the data blocks from the input to output buffer. Specifically, a process with the rank *i* rotates its data up by *i* blocks. The communication starts in a way such that, for all the *p* communicating processes, in each communication step k ( $0 \le k < \lceil \log_2 p \rceil$ ), process *i*, (i = 0, ..., p - 1), sends to ( $i + 2^k$ ) mod *p* (with wrap-around) all those data blocks whose *k*th bit is 1 and who receive from ( $i - 2^k$ ) mod *p*. The incoming data is stored into the blocks whose *k*th bit is 1. Finally, the local data blocks are shifted downward to place them in the right order. Fig. 2.1 shows *N* nodes with c = 8 cores arranged as two sockets and the total number of p = 8N processors performing the first four steps of the BIA. The rank placement is performed in block manner using consecutive core ordering. It can be observed that, until the *k*th step where  $2^k < c$ , the communication is still *intranode* for any core in the cluster. However, after the *k*th step, the communication becomes purely *internode* for all the participating cores.

If M is the data size to be exchanged in the all-to-all operation, then in each step, a process receives and sends  $\mathcal{L} = (M \times p)/2$  amount of data. Therefore, appropriate throttling levels

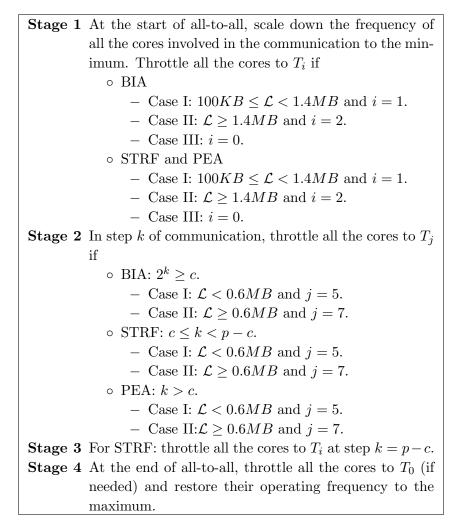

Figure 2.2 Energy saving strategy for the *all-to-all* operations with the throttling level selection based on the message size (per Table 1.1).

can be selected from Table 1.1 according to the communication type, given performance loss tolerance, and the message size.

"Send-To Receive-From" and Pairwise Exchange. For the block placement of ranks, in each step k  $(1 \le k < p)$  of STRF, a process with rank i sends data of size  $\mathcal{L} = M$  to  $(i+k) \mod p$  and receives from  $(i-k+p) \mod p$ . Therefore, for the initial and final c-1 steps, the communication is intranode while between these steps the communication is internode for any core in the cluster. The PEA uses *exclusive or* operation to determine the rank of processes for data exchange. It is similar to the BIA in terms of communication phase since after step kwhere k = c, the communication operation remains internode until the end.

Energy Saving Strategy. Because all three algorithms exhibit purely internode communications at a certain step k, the energy saving strategy as shown in Fig. 2.2 may be applied in stages to each of them. Following [38], the DVFS and CPU throttling policies are defined by the specific points within an algorithm where these techniques are applied and by a set of conditions indicating when to apply them. The invocation and the finishing point of the allto-all operation determine the stages where DVFS is applied and the proposed energy saving strategy defines the set of conditions as to how throttling is applied depending on the type (intra- or internode) of the given collective algorithm.

### 2.2 Allgather

MVAPICH2 uses three algorithms for performing allgather operation: 1) Bruck Concatenation algorithm for the nonpower of two number of processes and message size smaller than or equal to 1 KB, 2) Recursive Doubling algorithm for the power of two number of processes and message size larger than or equal to 1 KB, and 3) Ring algorithm for the message size greater than 1 KB and any number of processes. These algorithms are referred further in text as BCA, RDA, and RA, respectively.

**Bruck Concatenation Algorithm** copies the input data in each process to the top of the output buffer. Then, the communication phase proceeds as follows. In each step k, the process of rank i sends to the rank  $i - 2^k$  all the data it currently possesses followed by the receive operation from the rank  $i + 2^k$ . The data from the rank  $i + 2^k$  is then appended to the data already residing in the rank i. This procedure continues for  $\log_2 p$  steps. If the number of processes is not a power of two, an additional step is needed, such that each process sends the first  $(p - 2^{\lfloor \log_2 p \rfloor})$  blocks from the top of its output buffer to the destination and appends the data it receives to the data it already has. For BCA algorithm, in each step, a process receives and sends  $\mathcal{L} = (M \times p)/2$  amount of data.

**Recursive Doubling Algorithm.** In the first step, the processes that are a distanceone apart exchange their data of size M. In the second step, the processes that a distance-two

Stage 1 At the start of allgather, scale down the frequency of all the cores involved in the communication to the minimum. Throttle all the cores to  $T_i$  if • RDA and BCA: i = 0.  $\circ$  RA: - Case I:  $100KB \ge \mathcal{L} < 1.4MB$  and i = 1. - Case II:  $\mathcal{L} \geq 1.4MB$  and i = 2. - Case III: i = 0. **Stage 2** In step k of communication, throttle all the cores to  $T_i$ if • RDA:  $2^k \ge c$ . - Case I:  $\mathcal{L} < 0.6MB$  and j = 5. Throttle all the cores to state  $T_7$  for a step x > k where  $\mathcal{L} \geq 0.6MB.$ - Case II:  $\mathcal{L} \geq 0.6MB$  and j = 7. • BCA:  $2^k > c$ . - Case I:  $\mathcal{L} < 0.6MB$  and j = 5. - Case II:  $\mathcal{L} \ge 0.6MB$  and j = 7. **Stage 3** At the end of all-to-all, throttle all the cores to  $T_0$  (if needed) and restore their operating frequency to the maximum.

Figure 2.3 Energy saving strategy for the *allgather* operations with the throttling level selection based on the message size (per Table 1.1).

apart exchange their own data along with the data that they have received in the first step. In the third step, the processes that are a distance-four apart exchange their own data and also the data they have received in the previous two steps. Continuing in this manner, for a power of two number of processes p, all the processes receive all the data in  $\log_2 p$  steps. For a communication step i ( $i \leq \log_2 p$ ), the message size exchanged by each process is  $\mathcal{L} = 2^{i-1}M$ . Note that, until the kth step where  $2^k < c$ , the communication type is intranode for any communicating core while, after this step, the communication becomes purely internode.

**Ring Algorithm.** The data from each process is sent around a virtual ring of processes. In the first step, each rank *i* sends its contribution to rank i + 1 and receives the contribution from rank i - 1 (with wrap-around). From the second step onward each rank *i* forwards to rank i + 1 the data it received from rank i - 1 in the previous step. In each of p - 1 steps, a message of  $\mathcal{L} = M$  size is sent and received by each process.

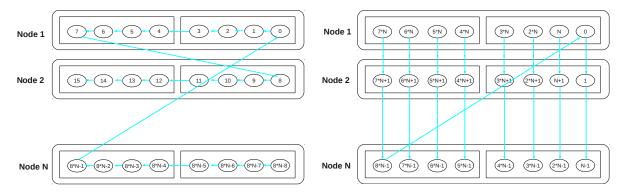

Figure 2.4 The RA communication pattern for the block (left) and cyclic (right) rank placements. Arrows indicate the communication direction.

**Energy Saving Strategy.** All the algorithms except the RA exhibit internode communication after a certain communication step. Therefore, the energy saving strategy outlined in Fig. 2.3 may be applied to each of them. The RDA and BCA are used for a message size smaller than 1 KB, therefore no throttling is applied for their intranode communication steps. Since the Ring Algorithm does not make purely internode communication at any step (see the left side of Fig. 2.4), the throttling level chosen at its start throughout the collective operation.

Rank Placement Considerations. The block rank placement calls for only two DVFS and up to four throttling switches in the proposed energy saving strategies. Hence, it minimizes the switching overhead. In the cyclic rank placement, however, after a fixed number of steps, the communication would oscillate between intra- and internode, and will require a throttling switch at every such step. Therefore, the block rank placement has been considered for the energy savings application.

In the RA implementation of the allgather operation, the communication is purely intranode for block and internode for cyclic rank placement as shown in Fig. 2.4. Thus, the cyclic rank placement does offer a better opportunity of applying a relatively higher level of throttling. However, it was found experimentally that, for RA, the allgather operation takes much less time to execute for the block rank placement compared with the cyclic one, so the energy saving potential has been foregone here in favor of the overall performance.

### CHAPTER 3. Runtime Procedure

In this chapter, a runtime procedure to obtain energy saving in point-to-point communications is discussed which proposes three frequency scaling strategies.

### 3.1 Runtime Communication Analysis

To apply frequency scaling in point-to-point communications, it is helpful to first categorize them as to the reappearances of rank sequences and message sizes; more generally, to determine the point-to-point *recurring patterns*. Then, by analyzing the obtained recurring patterns, it may be decided whether or not the frequency switching overhead is amortized and thus, whether or not the CPU frequency scaling is warranted. In this section, the ranks recurring during a certain time period are termed *sequence*, which together with its corresponding set of message sizes, is called *phase*. The length of a sequence measured as its number of point-to-point ranks is called the *phase length*. A phase can be uniquely identified by the rank and message size of the call that commences the phase. For each call in the phase, the parameters, such as call duration and time gap between the calls, are recorded to make the frequency scaling decisions.

Once the point-to-point communication phases are determined, they may be efficiently exploited for those applications that are based on iterative computations. Specifically, the frequency scaling is performed in the next iteration containing a given phase. All the chosen test applications exhibit an iterative behavior with point-to-point phases. However, if an application has no iterative communication, the sequence recognition will not be applicable.

The blocking point-to-point communications are selected in this work since reducing the processor frequency during their operation will not slow down the computational portion of the application and will result in a minimal system overhead as has been shown by the au-

Figure 3.1 Sequence recognition and phase grouping

thors earlier [53]. Specifically, paired communication primitives, MPL\_Send and MPL\_Recv, are considered here to explore the fundamental design aspects that may be applied to other MPI operations in the future. However, since non-blocking operations do not provide Infiniband CPU offload, this analysis cannot be extended for them. For tapping their energy saving potential, one may be able to employ only performance counters.

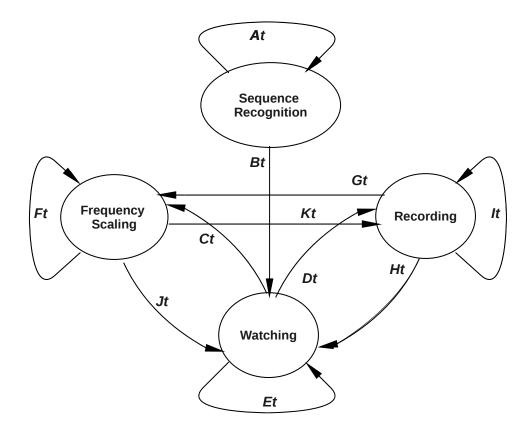

A general design of the runtime analysis procedure consists of four major states: *sequence* recognition, watching, recording, and application frequency scaling. Figure 3.2 outlines these four states along with their transitions, which are detailed in sections 3.1.1 to 3.1.4. The idea to use a state machine comes from the work of Freeh *et. al* [17], where a similar one was proposed.

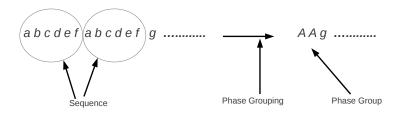

#### 3.1.1 Sequence Recognition

First, the initial recurring pattern of the ranks is to be determined, which may be achieved using a simple string matching algorithm performed during the application execution. Specifically, such an algorithm attempts to find two identical substrings of a certain length, after which a new sequence is declared as starting from the first matching rank and finishing with the rank preceding the start of the second identical substring. Figure 3.1 shows the sequence recognition process along with phase grouping. The point-to-point communication ranks are depicted by lower case letters and their sequences are enclosed into ovals. After recognizing the repeating pattern of the ranks, i.e, the sequence, the phase grouping takes place, which simply records maximal repeating substrings of phases as a group. For example in fig. 3.1, if an upper-case letter is assigned to depict a phase uniquely, then, a substring of the phases,

Figure 3.2 State diagram for runtime procedure to apply energy savings efficiently. The transitions are labeled with Lt, where L takes a value of the first 11 letters of the alphabet The transition of a state into itself (At, Et, Ft, It) indicate ongoing state action.

denoted as AA, forms group. Grouping of phases is important for certain frequency scaling strategies as discussed further in section 3.1.4.4. Alternatively, more sophisticated algorithms, such as the supermaximal repeat string algorithm [21], may be used. However, for simple rank patterns, those with a single maximal repeat string, and a moderate number of communicating processors this is not necessary. Note that a simple rank pattern means here that there is only a single sequence of ranks per each communicating process and that there are no other (out of sequence) calls between the end of one sequence and start of another. The substring length to match may be chosen experimentally, as was done in this work. As soon as the sequence is determined, the state changes to the watching state (transition Bt in fig. 3.2). Since this is the initial sequence, it is deemed to be also the first phase.

20

### 3.1.2 Watching

The aim of this state is to monitor call after call and, if certain conditions are met, attribute the current call to either the frequency scaling or the recording states. Specifically, in this state, the rank and the message size of the current call are compared with the information for the *first call* in all the previously recorded phases. Once a match, at least partial, is found the comparison is aborted and a state transition takes place as follows:

- If a complete match exists (i.e., both the rank and message size are matched), then go to the frequency scaling state since an occurrence of an existing phase has been found (Ct in fig. 3.2).

- If no complete match exists—only do the communicating ranks match,—then go to the recording state in search for a new phase (Dt in fig. 3.2).

Otherwise, the next call is considered in the watching state (Et in fig. 3.2).

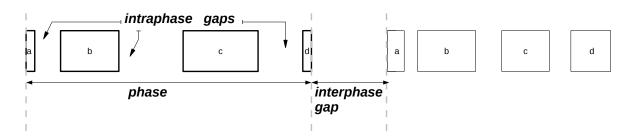

### 3.1.3 Recording

If only the rank matches some previously recorded phase but not the message size, then this may indicate the beginning of a new phase. The new phase then starts with the recording of the rank, message size, call duration, and time gap between each pair of the calls. In addition, depending on the chosen frequency scaling strategy (see section 3.1.4), the needed performance-counter values are recorded. Figure 3.3 provides an example of the recorded phases, where a phase is represented by calls a, b, c, and d. The time gap between successive phases is termed *interphase gap*, while a time gap within a phase is denoted as *intraphase*.

Simultaneously, the rank of the current call is checked against the corresponding rank within the initial sequence. If there is a mismatch, the recording of the new phase is aborted with two resulting state transitions:

- $\rightarrow$  frequency scaling, if *both* the rank and message size of the current call are equal to those of the first call in some previously recorded phase (*Gt* in fig. 3.2).

- $\rightarrow$  watching, otherwise (*Ht* in fig. 3.2).

If only the rank matches, then the recording state is re-entered for the next new phase recording

Figure 3.3 Trace of an MPI application invoking eight MPI\_Send and MPI\_Recv calls with a phase length of four. (The calls within a phase are ordered lexicographically from a to d.)

(It in fig. 3.2). Once a new phase is recorded, the transition to the watching state happens (Ht in fig. 3.2).

### 3.1.4 Frequency Scaling

In the frequency scaling state, the calls are continuously checked whether or not their communicating ranks match the *initial* sequence. If there is a mismatch, frequency of the processor is restored to its highest value  $f^{\text{max}}$  and the call causing the mismatch either remains in the current state (Ft in fig. 3.2), if both its rank and message size match the beginning of any already recorded phase, or enters the recording state (Kt in fig. 3.2), if only its rank matches. Otherwise, if both rank and the message size do not match, a transition to the watching state occurs (Jt in fig. 3.2).

The frequency scaling operation is performed such that frequency is reduced at the beginning of the phase and generally raised in the end of the phase. Three different strategies are discussed in the rest of section 3.1.4 for applying frequency scaling to the intra- and interphase time gaps.

### 3.1.4.1 Conservative Strategy

This strategy is applied if the interphase time gaps are conservatively assumed to be entirely compute-intensive, so their durations would scale linearly with the decrease in frequency. A performance loss  $\gamma$  must be defined (possibly by the user) to constrain the amount of the performance degradation that is tolerated when the CPU frequency is scaled down. In [58], an appropriate frequency is selected for a single (collective) communication call by taking into

account just the message size while exploiting the Infiniband CPU offload feature and certain communication characteristics. In the case of a multicall phase, the gaps between call pairs must be examined and evaluated as to their performance losses at a lower frequency.

Consider the execution at the highest frequency  $f^{\text{max}}$ . Then, let  $T_{call}(f^{\text{max}})$ ,  $T'(f^{\text{max}})$ , and  $T^{\text{max}}$  denote the total duration of the communication calls, of the intraphase time gaps, and of the entire phase, respectively, at the highest frequency, such that

$$T^{\max} = T_{call}(f^{\max}) + T'(f^{\max})$$

(3.1)

Let  $f_{\gamma}^*$  be a suitable frequency (as made available by a P-state) when the performance loss is  $\gamma$ ;  $O_{call}(f_{\gamma}^*)$  and  $O_s(f_{\gamma}^*)$  be the communication call and frequency switching overheads, respectively, when the frequency is changed from  $f_{\gamma}^*$  to  $f^{\max}$ . Then the desired available frequency  $f_{\gamma}^*$  is determined as

$$f_{\gamma}^{*} = \left\lceil \frac{T'(f^{\max}) \times f^{\max}}{\gamma \times T^{\max} - O_{call}(f_{\gamma}^{*}) - O_{s}(f_{\gamma}^{*})} \right\rceil,$$

(3.2)

where the ceiling operation is needed because the CPU provides only a number of P-states, among which the closest upper bound will be selected. This algorithm will work irrespectively of the specific number of P-states. The communication call overhead  $O_{call}(f_{\gamma}^*)$  varies with the message size and the inter- and intranode communication type, and its value may be taken as suggested in [53]. The frequency switching overhead  $O_s(f_{\gamma}^*)$  may be precomputed in advance for all the P-states in a given platform.

### 3.1.4.2 Intermediate Strategy

Since the intraphase time gaps may have architectural (resource-related) stalls, such as memory or I/O, an assumption of their high computational intensity may be too conservative in achieving maximum energy savings. Thus, a quantitative analysis is desirable to estimate the CPU usage between communication calls within a phase (i.e., during the intraphase time gaps). To this end, performance counters may be employed to measure the architectural stalls in modern processors. However, the number and applicability of these counters are typically limited. For example, the Intel Xeon E5450 processor, which is used in this work, provides only two general-purpose performance counters, and thus, hinders the construction of sophis-

ticated models, such as the one proposed in [23], which relies on four performance counters. Nevertheless, fewer counters are still useful if the frequency calculation is distilled to the most critical parameters that the available performance counters can measure. In particular, this work proposes to count both the micro-operations retired  $\mu\tau$  and memory accesses m mainly because the operation rate may be higher for memory-intensive applications than for computeintensive applications, which is counterintuitive without considering the memory accesses. By using an *a priori* analysis, the number of micro-operations retired  $\mu\tau(f^*)$  at an available CPU frequency  $f^* \mu\tau(f^*)$  has been predicted based on both  $\mu\tau(f^{\max})$  and  $m(f^{\max})$  [31] through the following relation:

$$\mu\tau(f^*) = \frac{f^* \times \mu\tau(f^{\max})}{f^{\max}} + b \times m(f^{\max}) , \qquad (3.3)$$

where the *b* is dependent on the number of memory accesses per second and was determined experimentally. Then, for the intraphase time gap  $t'_i$  (i = 0, ..., n - 1, where *n* is the number of calls in a phase),  $\mu \tau_i(f^*)$  may be determined and the corresponding performance loss  $\gamma_i$  for  $f^* < f^{\text{max}}$  calculated as

$$\gamma_i \approx \frac{\mu \tau_i(f^{\max}) - \mu \tau_i(f^*)}{\mu \tau_i(f^{\max})} \approx \frac{t'_i(f^*) - t'_i(f^{\max})}{t'_i(f^*)} .$$

(3.4)

Since the total overhead for executing the intraphase time gaps at a frequency  $f^*$  is  $O'(f^*) = T'(f^*) - T'(f^{\max})$  and by considering eq. (3.1) the suitable frequency  $f^*_{\gamma}$  may be calculated from

$$\gamma \ge \frac{O'(f_{\gamma}^*) + O_{call}(f_{\gamma}^*) + O_s(f_{\gamma}^*)}{T^{\max}} .$$

$$(3.5)$$

## 3.1.4.3 Shortcomings of Conservative and Intermediate Strategies

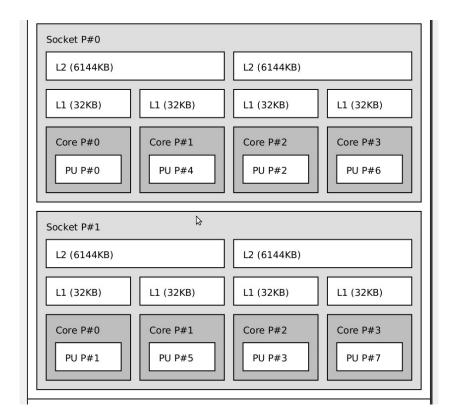

The conservative and intermediate strategies do not take into account application of frequency scaling in the interphase time gaps, which they assume to be computationally intensive. Additionally, they derive frequencies on a per-core basis. In practice, however, the DVFS is applied only in pairs of cores, i.e., in any two cores sharing an L2 cache, termed "twin cores" in

Figure 3.4 An Intel Xeon E5450 processor within one socket, having four physical cores. A physical core has an L1 cache and a shared L2 cache, such that pairs of core processing units (PUs)—(P#0, P#4), (P#2, P#6)—each share an L2 cache.

authors' previous work [54]. DVFS supports only a twin-core granularity on certain processors, meaning that it produces energy savings only when any two cores sharing the same L2 cache (as in fig. 3.4) are scaled to the same P-state. This was expected since the off-chip DVFS regulators are typical in current microprocessors [30]. Since cores are grouped around the L2 cache for the effectiveness of DVFS, the conservative and intermediate strategies are expected to work similarly in the case of three cache levels.

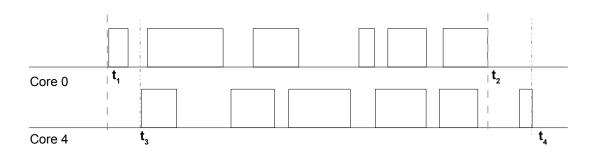

For the point-to-point communications, it is important to detect communication phases sufficiently long to be able to apply the dynamic frequency scaling without much overhead and to first determine a communication *phase overlap*  $\phi_o$ . Figure 3.5 illustrates how  $\phi_o$  is found for twin-cores 0 and 4. On core 0, the phase starts at time  $t_1$  and ends at  $t_2$ . Similarly for core 4, the phase starting and ending times are  $t_3$  and  $t_4$ , respectively. Then,  $\phi_o = (t_2 - t_3)/(t_4 - t_1)$ . Only if the value of this phase overlap is reasonably large does DVFS provide substantial energy savings for either conservative or intermediate strategies.

Figure 3.5 Overlapping of communication phases in a pair twin-cores that share the L2 cache. The phase boundaries are marked as vertical dashed and dash-dotted for core 0 and core 4, respectively.

Additionally, when the phase boundaries are assumed, as in [35], to simply be not sensitive to context—rather than compute intensive—meaning that their detection may not be known from the previous iterations, the frequency scaling is applied only for the MPI communication phases. For a single-core processor, such an approach may provide substantial energy savings. In a multicore system, however, if the application communications exhibit very low phase overlap, it may not save any energy, similarly to the conservative or intermediate strategy when used without the phase overlap consideration in twin cores.

#### 3.1.4.4 Aggressive Strategy

To overcome the often tedious provisioning for the phase overlap in multicore platforms, an aggressive strategy is proposed here, so that it targets interphase time gaps for frequency reduction and extends to them the performance-counter usage of the intermediate strategy. Specifically, it calculates the micro-operations retires and memory accesses in the interphase gaps and applies to them an appropriate frequency  $f_{\gamma}^*$  in a manner similar to that of the intermediate strategy. Then, the performance loss is calculated as in eq. (3.4).

Once a phase ends, the current frequency  $f^c$  is compared with  $f^*_{\gamma}$  and is left unchanged if they are the same. Otherwise,  $f^c$  takes the value of  $f^*_{\gamma}$  if, in addition, the switching overhead  $O_s(f^*_{\gamma})$  is less than the performance overhead  $O''(f^c)$  from executing the interphase gap at the current frequency  $f^c$ . By considering the switching and performance overheads during the